Процессор Cell: "клетка" PC будущего или слон из мухи?

О новом процессоре под кодовым названием "Cell" (в дословном переводе — ячейка, клетка), пожалуй, так или иначе слышали все. Но слышали, скорее всего, немногое: процессор на модифицированной RISC PowerPC архитектуре, изначально ориентированный на использование в составе объединенных Cell- структур, с достаточно высокой заявленной производительностью — стратегический альянс Sony, IBM и Toshiba (SIT) не слишком распространялся о своем детище. Однако по мере приближения работ над чипом к завершению в различных СМИ всплывало все большее количество информации о Cell; кульминацией стали доклады представителей SIT на специализированной конференции ISSCC 2005, где широкой публике были представлены первые официальные технические данные о "процессорной клетке".

Собственно, данный материал — результат сбора, обработки и анализа всей этой, порой довольно противоречивой, информации из множества официальных и неофициальных источников. Я расскажу об истории создания, архитектуре (по крайней мере, об известных ее элементах), планируемых областях применения, а также о плюсах и минусах этого как минимум любопытного чипа. Не исключено, что он станет достойной альтернативой (заменой? дополнением?) существующим и готовящимся к выпуску многоядерным х86-процессорам AMD/Intel, основополагающим элементом будущей бытовой техники цифрового дома или, по меньшей мере, надежным и быстрым "сердцем" Sony PlayStation 3. Впрочем, о перспективах чипа речь пойдет чуть позже, пока же предлагаю оглянуться в недалекое прошлое и вспомнить как этапы разработки самого Cell, так и жизненный путь его "идейных предшественников". А ведь это, между прочим,

Cellая история

Компьютерщики со стажем, глядя на восторженные крики в специализированной и не очень прессе ("256 GFLOPS — и это производительность лишь одного "восьмиядерного" чипа!") и очередные пророчества скорой смерти PC (архитектура IA-32, также известная как "x86"), наверняка тихо посмеиваются, вспоминая, как 10-15 лет назад RISC-процессоры (DEC Alpha, IBM POWER, Sun SPARC) казались несомненными "убийцами" своих CISC-собратьев (486, Pentium). И что же? Несмотря на то, что последние CISC-процессоры позаимствовали многое из RISC-архитектуры (припомним хотя бы Pentium 4 с его micro-ops'ами), они по-прежнему продолжают доминировать на рынке, оставляя для RISC достаточно узкую нишу специализированных высокопроизводительных решений, а также рынка Apple Macintosh. Почему же более производительные RISC-процессоры не выдержали конкуренции с CISC?

Для начала разберемся с терминологией. CISC — это Complex (Complete) Instruction Set Computing (Полный Набор Команд). Формально к этому классу относятся в большей или меньшей степени все нынешние Athlon'ы, Pentium'ы и прочие процессоры для IBM PC совместимых компьютеров. В большей или меньшей потому, что те или иные заимствования идей и методов RISC имеются практически в каждом современном чипе. RISC — это Reduced Instruction Set Computing (Уменьшенный Набор Команд). Собственно название говорит само за себя: на основе статистического анализа кода множества CISC- приложений определяются наиболее часто используемые команды; уменьшение же числа команд позволяет увеличить число внутренних регистров (пересылка между регистрами выполняется быстрее всего), сделать конвейер более эффективным и поднять частоту его работы (чем более простые команды в нем исполняются, тем выше частота). Несмотря на значительно увеличившийся объем программного кода, RISC-процессор будет работать в несколько раз быстрее CISC-собрата с одинаковой частотой: специалисты всегда предпочтительнее универсалов (в плане быстродействия — уж точно). Разницу между RISC- и CISC-программами можно пояснить на простом примере. Но для начала оговорим некоторые детали: память компьютера адресуется по номеру строки и столбца, из которого осуществляется выборка (или в который производится запись). Операции над значениями из памяти производятся в исполнительном блоке, который, однако, может работать лишь с данными, загруженными в процессорные регистры. Пусть нам нужно умножить два значения в памяти по некоторым адресам 2:2 (строка:столбец) и 5:4. CISC нацелен на исполнение задачи при минимуме команд: набор инструкций процессора строится таким образом, чтобы все более или менее сложные действия решались одной командой. Предположим, что в CISC- процессоре имеется команда MULT, которая выбирает указанные значения из ячеек памяти, записывает их в различные регистры и сохраняет результат в соответствующем регистре. Тогда задача умножения решится в одну строку кода:

MULT 2:2, 5:4

RISC-процессоры используют простые инструкции, которые исполняются за один такт. В этом случае вместо MULT потребуются команды LOAD/STORE, загружающие данные из памяти в регистр и записывающие их обратно, а также команда PROD, выполняющая умножение данных в двух некоторых регистрах. Эквивалентом MULT для RISC-процессора будет следующий код:

LOAD A, 2:2

LOAD B, 5:4

PROD A, B

STORE 2:3, A

Таблица 1. Различия CISC и RISC

В принципе, с увеличением объема кода можно мириться, если этот самый увеличенный объем позволит в несколько раз повысить быстродействие — пишут ведь на ассемблере? Пишут! Кроме того, RISC-код очень эффективно "распараллеливается"... В чем тогда причина непринятия RISC'а рынком IBM PC? Во- первых, как несложно догадаться, наборы инструкций CISC и RISC несовместимы. CISC-кода для PC-программ было написано очень много, а вот любителей писать под RISC на порядки меньше. Создавались, конечно, эмуляторы, автоматически транслирующие CISC-инструкции в RISC (подобные техники для увеличения скорости обработки используется в современных CISC-процессорах), но работали они настолько медленно, что разница в производительности между настоящими и эмулированными CISC практически сводилась к нулю. Таким образом, эмулировать CISC на RISC-процессорах оказалось неэффективно, а главное — экономически нецелесообразно.

Во-вторых, как следствие сыграла свою роль несовместимость ПО. Для х86 уже были написаны DOS и набирающая популярность Windows, а различные RISC- процессоры ютились на Unix, причем, как правило, на несовместимых между собой ее воплощениях. Да и программ для них было куда меньше, особенно пользовательских — все больше научные, специализированные.

В-третьих, несмотря на кажущуюся "упрощенность", RISC-процессоры были дороги — они выпускались сравнительно небольшими партиями для высокопроизводительных рабочих станций, и производители не считали нужным ни экономить на материалах, ни совершенствовать/оптимизировать дизайн, ни упрощать чипсет и материнскую плату. Крупные компании вроде Sun или DEC даже не задумывались об этих "мелочах", наивно полагая, что альтернативы их решениям отсутствуют. В некоторых сферах (научные ресурсоемкие вычисления), действительно, конкурировать с RISC системам на базе CISC-процессоров было сложновато. Зато во всех остальных недорогие и достаточно производительные x86-процессоры остались "на коне".

Тем не менее, жажда обойти Intel не давала покоя крупным полупроводниковым компаниям, и в 1991 году Apple, IBM и Motorola основали альянс AIM Alliance, который немедленно занялся созданием дешевого, быстрого и современного RISC-процессора. В 1993 году была представлена спецификация платформы PowerPC, а также первый чип — 32-разрядный PowerPC 601, работавший на частотах 50 и 66 МГц. Название PowerPC пошло от многочиповой RISC-архитектуры IBM POWER, на базе системы команд которой и был основан первый процессор. Чип рассеивал намного меньше тепла, чем его конкурент в лице Intel Pentium, и работал зачастую быстрее его. Вслед за 601-м появились 603/604 модели, затем в 1997 — PowerPC 750 (G3) с L2-кэшем и ускоренной системной шиной. В 1999 модельная линейка процессоров PowerPC пополнилась PowerPC 7400 (G4) — "конкурентом" Intel Pentium III, представившим поддержку набора команд для векторных вычислений AltiVec (также известного как VMX — Vector Multimedia eXtension — эдакое "мультимедийное расширение" PowerPC). Однако с появлением и совершенствованием архитектуры Intel NetBurst (в Pentium 4) процессоры компании закрыли единственное слабое место, которое позволяло PowerPC выглядеть более выигрышно: заметно ускорив операции с плавающей точкой, х86- процессоры оказались самыми быстрыми и дешевыми на рынке. PowerPC-чипы же остались уделом Apple Macintosh да различных встраиваемых систем (благодаря низкой рассеиваемой мощности) — системы на их базе, даже с учетом более дешевого процессора, все равно получались заметно дороже IBM PC совместимых компьютеров. Кардинальным образом ситуацию не изменил и выход нового процессора от IBM — PowerPC 970 (G5). Он позволил лишь приблизиться к x86 фаворитам в некоторых приложениях (и даже порой опережать их в оптимизированных), но не более того. Впрочем, не исключено, что герой этой статьи The Cell сможет вернуть RISC'у пальму первенства и создать предпосылки для появления популярной альтернативы долгоиграющей x86.

Пожалуй, один из главных инициаторов создания The Cell — подразделение Sony под названием Sony Computer Entertainment Inc. Еще с момента выпуска Emotion Engine ("сердца" PlayStation 2) SCEI не давали покоя мысли по более широкому его применению: например, объединение нескольких [десятков] EE демонстрировало солидную по тем временам (2000 год) производительность. Впрочем, прототип "числоперемалывателя" GSCube на основе 16 пар Emotion Engine и Graphics Synthesizer с 2 Гб RAM и 512 Мб видеопамяти оказался невостребованным из-за высокой цены и неавтономности (ему требовался для работы управляющий сервер SGI Origin 3400). Тем не менее, образованный в 2000 альянс IBM, Sony и Toshiba, засучив рукава, взялся за разработку не только мощного процессора для Playstation 3, но и универсального, многоцелевого и очень производительного продукта под кодовым названием Cell. Центр по разработке открылся на год позже (2001 г.) в Остине, штат Техас. Примерно в это же время, в марте 2001, патентное бюро США зарегистрировало патент и заявку на патент, в самых общих чертах описывавшие принципы функционирования Cell-структур. Изобретателями значились руководящие сотрудники SCEI, а правопреемниками — представители Toshiba и IBM.

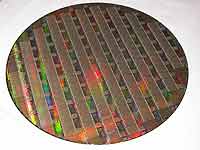

Jim Kahle (IBM) с коллегами из Toshiba и SCEI демонстрирует пластину Cell

Jim Kahle (IBM) с коллегами из Toshiba и SCEI демонстрирует пластину Cell

IBM предоставила давнему дуэту по разработке специализированных чипов для Playstation в лице Sony и Toshibа свой солидный багаж технологий в области (в частности, метод"кремний-на-изоляторе" (Silicon On Insulator — SOI) для ускорения создания сверхмощных процессоров класса "система на чипе" (System On Chip — SOC). Ну и, конечно, производственные мощности. Sony с Toshiba — подключили лучшие умы для реализации интересных идей и наработок. Собственно, теперь, когда более четырех лет разработки (и миллиард с небольшим долларов, потраченный только на R&D) позади, а чипы уже производятся в ограниченных количествах на фабрике IBM в East Fishkill, когда информационный "железный занавес" троицы гигантов начал понемногу раздвигаться, можно поговорить о чипе более подробно. Несмотря на то, что сплошным "гаданием на кофейной гуще" (как в ранних зарубежных "аналитических материалах"), конечно же, нижеприведенная информация о структуре Cell не является, многие моменты (особенно связанные с реальным коммерческим воплощением чипа) остаются не проясненными до конца. Этот год обещает быть богатым на новости, связанные с Cell (особенно если учесть планируемый анонс Playstation 3 в мае), но не думаю, что фундаментальные концепции архитектуры будут изменены. Впрочем, довольно разговоров, пора уже взглянуть на

Сell изнутри

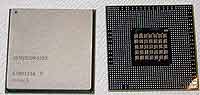

"Суперкомпьютер на чипе", как назвала Cell SIT в своей ISSCC-презентации, производится по 90 нм SOI-технологии с применением low-k-диэлектрика и восьмислойных межсоединений (low-k Intel реализует лишь в 65 нм техпроцессе c 7-ю слоями межсоединений). Первые тестовые образцы Cell представляют собой запакованные в стандартный BGA-корпус 42,5х42,5 мм (1236 контактов, из них 506 сигнальных, остальные — земля/питание) 234 млн транзисторов, образующих 9 "ядер" — основное, базирующееся на архитектуре PowerPC (PPE — Power Processor Element) и 8 векторных "доппроцессоров" (SPE — Synergistic Processor Element); остальные транзисторы реализуют интерфейс контроллера ввода/вывода (Flex I/O BIC, Bus Interface Controller) и памяти (MIC — Memory Interface Controller), а также, конечно, связывающую все элементы воедино внутреннюю шину (EIB — Element Interconnect Bus). Все это безобразие работает на частотах от 4 ГГц (хорошо, "должно работать на частотах от 4 ГГц";)) при напряжении питания от 1 В, обеспечивая при вычислениях с одинарной точностью (single precision) производительность более 256 гигафлопс!!! Если вы еще не свалились со стула, сообщу, что, к примеру, система на паре Intel Itanium 2 1,5 ГГц, демонстрирует лишь около 11-12 ГФлопс (миллиардов операций с плавающей запятой в секунду), а AMD Opteron 1,8 ГГц — около 4. Впрочем, к этой цифре (256 ГФлопс) стоит относиться с известным скептицизмом, однако даже если предположить, что SIT завысили реальную производительность (измерять ведь можно по-разному) в 10 раз, то все равно 25,6 ГФлопс для одного небольшого и легкомасштабируемого чипа — впечатляющее достижение.

Таблица 2. Сравнение характеристик прототипа Cell и современных х86-процессоров

Cell изначально ориентирован на работу в симбиозе с другими "клетками". В идеале это выглядит так: когда Cell'ы некоторых объединенных в единую сеть устройств начинают простаивать, Cell'ы наиболее загруженных устройств перекладывают на "отдыхающих" часть своей работы, что выливается в заметное повышение производительности. Представьте, к примеру, что Cell'ам рабочей станции в сложном рендеринге "помогают" их собратья из игровой приставки, цифрового видеомагнитофона, ноутбука... Да, пока это кажется фантастикой, но все предпосылки для реализации "цифровой идиллии" есть. В теории возможности объединения аппаратных "клеток" не ограничены. А специально для обмена информацией между ними используются программные "клетки" — так называемые апулеты (APUlets, произошедшие от прежнего названия SPE — Attached Processor Unit, т.е. присоединенный процессор) — по большому счету, блоки, содержащие данные и описание тех действий, которые над этими данными необходимо произвести. Технология отдаленно напоминает программы распределенных вычислений типа SETI@Home, однако в каждом апулете будут содержаться не только данные для обработки, но и сам клиент-обработчик.

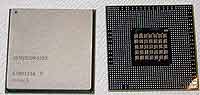

Первые пилотные экземпляры Cell

Первые пилотные экземпляры Cell

Рассмотрим все структурные элементы чипа по отдельности в подробностях (насколько это позволяют доступные источники информации). Итак, "ядром" каждой "клетки" является Power Processor Element, он же PPE. О ключевом элементе Cell'а, обеспечивающем "нагрузку" и управление SPE, взаимодействие с ОС, а также прочими "побочными" вычислениями, к сожалению, пока известно немногое. Это нечто выполненное на базе "64-битной Power-архитектуры" (на базе PowerPC 970? POWER 5? чего-то принципиально нового?) с поддержкой набора векторных мультимедийных расширений AltiVec и технологии многопоточности SMT (Simultaneous Multi-Threading) — судя по всему, некий аналог Hyper-Threading'а от Intel. PPE Cell, в отличие от последних x86-процессоров, не форсит мегабайтами кэша, но, похоже, 64 Кб L1-кэша (32 Кб для инструкций, 32 Кб — для данных) и 512 Кб L2-кэша ему вполне достаточно для получения приемлемой производительности.

PPE заправляет восьмью SPE, или Synergistic Processor Element. Эти "синергические" процессоры, по сути, являются специализированными независимыми векторными процессорами. Может возникнуть вопрос: что же это за векторные вычисления такие? В программистском понимании вектор — это упорядоченный список скалярных (-5, -3,999(9), 5.61, 18 и т.д.) значений. Соответственно, если мы работаем с векторами (массивами), то можем выполнять операцию над множеством данных одной инструкцией — это и называется SIMD (Single Instruction Multiple Data — один поток команд, множество потоков данных). Идея SIMD давно и успешно применяется как в специализированных системах, так и в Mac'ах (AltiVec), и в PC (SSE-SSE3, 3DNow!...). Продемонстрируем удобство векторных вычислений на вполне жизненном примере. Итак, пусть у нас имеются три вектора-массива по N элементов в каждом: А, В и C. Необходимо сложить соответствующие значения в массивах А и В, записав результат в массив С. Если код не будет "векторизован" компилятором, то процессор будет поочередно выбирать по одному значению из А с В, затем складывать эти значения, записывать результат в С, выбирать следующее значение из А с В... И так — N раз. Если же код будет векторизован, процессор сможет не тратить "лишние" такты на манипуляции с единичными значениями; векторы А и В будут считаны из памяти целиком, операция векторного сложения их сложит "единовременно" (c минимальной задержкой на поступление очередной пары значений в вычислитель), а по окончании операции вектор-результат С будет записан в память "за один присест".

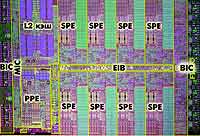

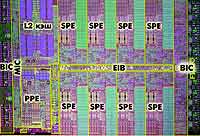

Внутреннее строение Cell

Внутреннее строение Cell

Если подключить воображение и предположить, что с векторами нужно проделать не одну, а несколько операций (это актуально для графических приложений с различными матричными преобразованиями), то выигрыш в производительности благодаря "одновременной" работе со всеми значениями становится очень и очень значительным. Тем не менее, далеко не всякий код можно "векторизовать": препятствием на пути солидного ускорения станет и одномерная рекурсия, и сложные условные переходы, и специфичность алгоритмов... В общем, векторизация и векторные вычисления — вещь хорошая, позволяющая достичь большой скорости исполнения программы... но лишь в тех случаях, когда код под это "заточен". В противном случае никаких дивидендов от векторных команд добиться не получится.

Но вернемся к нашему "восьмиединому" векторному SPE. По сути, он представляет собой классический векторный (но, в отличие от традиционных "векторников", независимый) процессор с длиной команды в 32-бита и размером вектора в четыре 32-битных слова. При этом каждое из слов обрабатывает "свой" целочисленный блок или блок по работе с плавающей запятой (FPU — Floating Point Unit). Каждый SPE обладает 128 (!) 128- разрядными регистрами и небольшим объемом (256 Кб) локальной памяти, разделенной на 4 адресных пространства по 64 Кб. Так как память фактически объединена с процессором, вопрос кэша для выравнивания их (процессора с памятью) производительности не ставится. Но хватит ли 256 Кб для эффективной обработки апулетов? По идее, этого объема должно быть вполне достаточно (а для апулетов-шейдеров — и подавно), но пока делать окончательные выводы рановато. С внешней же памятью SPE может "общаться" через Memory Interface Controller с применением механизма DMA (Direct Memory Access — прямой доступ к памяти) — то есть напрямую, без посреднических услуг PPE. Ну и для завершения "портрета по фотографии" основной движущей силы Cell — Synergistic Processor Element'а — необходимо добавить, что каждый SPE можно динамически "закрывать" и "открывать" для защиты внутренних ресурсов от доступа извне (опять-таки, точный принцип действия этого механизма пока неизвестен), а также что SPE в своем наборе инструкций не имеет поддержки AltiVec (VMX). Следовательно, общая производительность при использовании этих расширений будет определяться лишь одним PPU. Возможно, при этом будут задействованы и SPE, но "родная" поддержка векторного набора команд упростила (и ускорила) бы процесс. Таким образом, SPE представляет собой достаточно мощный, но в то же время узкоспециализированный процессор. Если программист (при помощи компилятора) сумеет добиться от него полной отдачи, эффективно загрузив "апулетами", производительность резко подскочит. В противном случае, боюсь, при исполнении невекторизованного кода заметного прироста производительности даже от 16 SPE (по большому счету, количество SPE в Cell ограничивается лишь технологическими ограничениями при производстве кристаллов) ждать не стоит.

Все ключевые элементы чипа (8 SPE, PPE, MIC и BIC) cвязаны между собой высокоскоростной шиной EIB — Element Interconnect Bus. Она четырьмя кольцами "опоясывает" все блоки структуры, позволяя передавать до четырех 128-битных слов одновременно (!!!) с пиковой пропускной способностью 96 байт/сек. Именно с ее помощью апулеты из PPE "разбрасываются" по SPE или кочуют между ними, отправляясь по мере готовности в память. Шина EIB позволяет инженерам гибко наращивать число SPE в случае необходимости (для модифицированных версий чипа, очевидно).

Структурная схема Cell-чипа

За связь с "внешним миром", а в частности — с таким важнейшим элементом, как RAM (т.е., оперативная память), отвечает Memory Interface Controller, или MIC. Для своего детища инженеры SIT лицензировали сверхбыструю XDR RAM от Rambus (да, уже можно представить, сколько ЭТО будет стоить). Двухканальная XDR RAM на 4-х чипах позволит обеспечить пропускную способность порядка 25 Гб/сек! Кроме того, контроллер умеет закрывать доступ к определенным фрагментам памяти конкретным SPE. К сожалению, пока на рынке представлены максимум 512 Мбит чипы памяти, а следовательно — общий объем RAM не сможет превысить 256 Мб. Однако ходят слухи о том, что контроллер XDR RAM может работать и в другом ("серьезном") режиме, поддерживая до 32 Гб памяти с коррекцией ошибок (ЕСС). Впрочем, за столь высокую скорость (традиционная PC3200 обеспечивает пропускную способность лишь порядка 3,2 Гб/сек) неизбежно приходится платить. В данном случае — предсказуемо высокой ценой и сравнительно небольшой емкостью чипов. Контакт с внешними устройствами (и, похоже, с другими Cell) обеспечивает еще одна лицензированная разработка Rambus — шина Flex I/O и ее контроллер Bus Interface Controller. Она обеспечивает огромную пропускную способность (44,8 Гб/сек на передачу, 32 Гб/сек на прием), а также использует фирменные технологии снижения тепловыделения DRSL (Differential Rambus Signaling Level — дифференциальный уровень сигналов Rambus) и упрощения топологии схемы FlexPhase. Очевидно, что для Cell имеются хорошие возможности для объединения — было бы с чем;)! Все чипы, работающие на высоких частотах, неизбежно сталкиваются с одной проблемой — тепловыделением. Будь процессор хоть трижды суперпроизводителен, он вряд ли получит распространение в мире, если для его охлаждения потребуется установка на жидком азоте. Контролируют питание, нагрев и энергопотребление Сell'а встроенная система динамического управления мощностью Dynamic Power Management (DPM автоматически выбирает одно из пяти состояний управления питанием), а также 10 цифровых и один линейный термодатчик. Так что гибкости и средств мониторинга Cell'у явно не занимать. При этом, по неофициальной информации, 4 ГГц чип рассеивает 80 Вт (1,1 В), а старший 5,3 ГГц вариант (1,3 В) — 180 Вт. С переходом на более совершенный 65 нм техпроцесс SIT планируют снизить тепловыделение до 30-40 Вт для 4,6 ГГц чипа Cell. И такие цифры (как тактовой частоты, так и рассеиваемой мощности) выглядят, разумеется, крайне привлекательно.

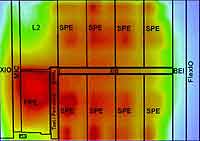

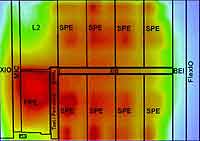

Тепловыделение различных блоков Cell под нагрузкой

Тепловыделение различных блоков Cell под нагрузкой

Что можно сказать в заключение "брифинга" по архитектуре The Cell? Процессор, безусловно, обладает рядом интереснейших особенностей, позволяющих прочить ему большое будущее. Мощнейший контроллер памяти, "бесконечная" расширяемость, многоядерность, технология апулетов и раздельных спецпроцессоров... Пока (и, к сожалению, лишь на бумаге) The Cell выглядит впечатляюще. Не стоит забывать, однако, сколько раз амбициозные высказывания разработчиков оказывались, гхм, "преувеличенными", а также сколько раз непобедимую глыбу CISC безуспешно пытались "убить" RISC- процессоры. Да, на оптимизированном коде по производительности вряд ли кто-то сможет что-то противопоставить Cell, но как быть с обыкновенными, не оптимизированными, приложениями? С огромным количеством CISC-программ? Будут ли они эмулироваться, переноситься? Насколько это будет выгодно с экономической точки зрения?.. Кроме данных насущных вопросов, уверен, всплывет и еще одна извечная проблема RISC — цена. Очевидно, что Cell — очень сложный чип, да и компоненты для него вряд ли будут простыми и дешевыми (одна память чего стоит!). Поэтому возникает основополагающий вопрос: сможет ли SIT производить Cell в таких количествах, чтобы удерживать цены на разумном и конкурентоспособном уровне? Судя по тому, что Playstation 3 вряд ли будет стоить более 500 у.е. даже в первые месяцы, сам Cell не будет очень уж дорог — Sony нет смысла работать себе в убыток. Впрочем, не будем гадать, а лучше поговорим о возможных сферах применения Cell и сделаем предварительные оценки его потенциала в каждой из областей.

Cell'и Cell'а

Первой и важнейшей (для SCEI;)) сферой применения нового чипа станет давно ожидаемая (но до сих пор не анонсированная) игровая приставка нового поколения — Sony Playstation 3. По слухам, в ней будут работать аж 4 Cell'а на тактовой частоте 4,6 ГГц. Честно говоря, это выглядит слишком фантастично; куда реальнее будет наличие одного 4-гигагерцевого Cell'а и низковольтной "клетки поддержки". Дело в том, что четыре 4,6 ГГц Cell'а будут рассеивать вкупе с мощнейшим графическим чипом... гхм... очень много тепла. Сомнительно, что Sony станет позиционировать PS3 еще и в качестве портативного обогревателя;) — именно поэтому, скорее всего, количество Cell будет ограничено. В противном случае Sony придется применять уж очень нестандартные охладительные решения, чтобы эффективно отводить около 500 Вт, выделяемых всеми этими замечательными устройствами. Но даже если в PS3 будет один Cell, его производительности создателям игр хватит надолго. Ведь фактически каждый SPE есть подобие Emotion Engine из PS2, да еще и с "бесплатным приложением" в форме PPE... На мой взгляд, SPE смогут достаточно уверенно работать с вершинными шейдерами, заниматься обсчетом игровой физики, звука, а на PPE будут возложены "задачи поддержки". Пусть эффективно программировать Cell, скорее всего, будет не легче, чем EE+GS (PS2), мучения программистов с лихвой будут компенсированы огромным вычислительным потенциалом "клетки". PS3 наверняка сможет уверенно работать с DVD, видео, телевидением высокой четкости (HDTV — High Definition TeleVision) а также прочими "цифро- домашними" приложениями.

Как следствие еще одно важное направление для применения чипа (в котором заинтересована не только Sony, но и Toshiba) — бытовая электроника. "Умные" видеомагнитофоны, исключительно "сообразительные" телевизоры, недорогие и высокоэффективные мультимедиацентры... Простор для использования Cell на этом поприще удивительно широк. Разумеется, светлое будущее ждет новые чипы лишь в том случае, если они будут: а) сравнительно недороги, б) "холодны" и в) сопровождаться удобным инструментарием для программирования.

Далее. Cell'ы отлично будут чувствовать себя в специализированных рабочих станциях и "недорогих" суперкомпьютерах. Благодаря отличной заявленной масштабируемости и производительности для задач, скажем, специфической визуализации, разнообразных ray-tracing-алгоритмов, научных вычислений (даже с двойной точностью) Cell сможет прочно обосноваться и в этой нише. Опять-таки, для этого необходимо соблюдение многих условий (например, решение вопроса с объемом памяти), но так или иначе вероятность того, что чип приживется в традиционно RISC'овой нише крайне велика. Несмотря на обилие "специалистов", прочащих Cell в очередные "убийцы х86", очевидно, что платформе Wintel в ближайшее время ничто не угрожает. В идеальном для SIT случае Cell'ы постепенно вытеснят продукты Intel/AMD с рынка. Однако для достижения этого необходимо преодолеть большое количество "но": Cell должен или быстро обзавестись собственным большим набором софта, или научиться очень эффективно эмулировать CISС; кроме того, должен быть создан удобный и эффективный инструментарий для создания программ (желательно — язык высокого уровня), позволяющий использовать преимущества архитектуры Cell "по полной". Вдобавок, повторюсь, Cell-системы должны продаваться если не по низким, то хотя бы по средним (до 1000 у.е.) ценам — дорогие и несовместимые системы х86 пережует и выплюнет вообще безо всяких усилий. Значительно более вероятно, что на РС Cell будут успешно применяться в качестве специализированных прикладных "числодробилок". Например, для цифровой обработки сигналов (алгоритм быстрого преобразования Фурье легко векторизуется), графических нужд (при необходимости Cell, судя по всему, сможет успешно работать в качестве GPU), аудиообработки — PCI Express карта расширения с чипом (-ами) Cell послужит хорошим дополнением к Pentium'у/Athlon'у. Но, опять- таки, для этого нужен серьезный инструментарий для разработчиков (говорят, IBM активно работает над SDK), качественные драйверы, разумные цены... Перспективно ли это? Безусловно! Возможно ли это? Пока трудно сказать. Если SIT планируют серьезно двигать свое детище в массы — разумеется, да. Если же после дебюта в PS3 SIT развитие Cell затормозят (по всем направлениям), то на эттом чипе можно будет смело ставить крест.

300 мм "многоклеточная" пластина

300 мм "многоклеточная" пластина

Как минимум еще одна компания должна в данный момент тщательно изучать Cell — это Apple Computers. Так как IBM пока еще работает над последователем мощного PowerPC 970, Cell может стать неплохой альтернативой для применения в Mac'ах. А может и, чем Джобс не шутит, достойным G6. Cell поддерживает AltiVec (VMX) — пусть производительность этих расширений вряд ли будет выдающейся (т.к. обрабатывать их умеет лишь PPE) — Apple наверняка сможет получить свои дивиденды от архитектуры Cell — масштабируемости, производительности, многопоточности и многоядерности.

Новый бестcellер?

К сожалению, на вопрос, вынесенный в заголовок статьи, еще нельзя ответить однозначно. Да, "стелит" альянс гигантов мягко, но вот будет ли так же мягко "спать"? По характеристикам, идеям и технологиям Cell — однозначный прорыв в микропроцессорной индустрии. Впрочем, направление прорыва станет известно позднее;). Станет ли Cell обыденным компонентом бытовой техники? Найдет ли применение в рабочих станциях? Останется ли "замурованным" в Playstation 3? Попадет ли под крыло Apple? Сможет ли стать хорошим строительным материалом для создания суперкомпьютеров? "Убьет", будет смят или сумеет мирно сосуществовать с x86-процессорами?.. Каким образом разрешится эта интрига, а также кто из аналитиков- Нострадамусов, задающихся подобными вопросами, окажется прав, мы узнаем в ближайшие пару лет. А пока можно констатировать лишь одно: на стапелях SIT разрабатывается и уже производится крайне интересный продукт, который, возможно, перевернет устоявшийся рынок микропроцессоров. Возможно, однако, что чип будет столь же "популярен", как и Emotion Engine PlayStation 2 и многие другие RISC-продукты... Поживем — увидим! Так что следите за новостями — теперь слово "Cell" будет мелькать в них все чаще и чаще!!

Николай "Nickky" Щетько,me@nickky.com

Собственно, данный материал — результат сбора, обработки и анализа всей этой, порой довольно противоречивой, информации из множества официальных и неофициальных источников. Я расскажу об истории создания, архитектуре (по крайней мере, об известных ее элементах), планируемых областях применения, а также о плюсах и минусах этого как минимум любопытного чипа. Не исключено, что он станет достойной альтернативой (заменой? дополнением?) существующим и готовящимся к выпуску многоядерным х86-процессорам AMD/Intel, основополагающим элементом будущей бытовой техники цифрового дома или, по меньшей мере, надежным и быстрым "сердцем" Sony PlayStation 3. Впрочем, о перспективах чипа речь пойдет чуть позже, пока же предлагаю оглянуться в недалекое прошлое и вспомнить как этапы разработки самого Cell, так и жизненный путь его "идейных предшественников". А ведь это, между прочим,

Cellая история

Компьютерщики со стажем, глядя на восторженные крики в специализированной и не очень прессе ("256 GFLOPS — и это производительность лишь одного "восьмиядерного" чипа!") и очередные пророчества скорой смерти PC (архитектура IA-32, также известная как "x86"), наверняка тихо посмеиваются, вспоминая, как 10-15 лет назад RISC-процессоры (DEC Alpha, IBM POWER, Sun SPARC) казались несомненными "убийцами" своих CISC-собратьев (486, Pentium). И что же? Несмотря на то, что последние CISC-процессоры позаимствовали многое из RISC-архитектуры (припомним хотя бы Pentium 4 с его micro-ops'ами), они по-прежнему продолжают доминировать на рынке, оставляя для RISC достаточно узкую нишу специализированных высокопроизводительных решений, а также рынка Apple Macintosh. Почему же более производительные RISC-процессоры не выдержали конкуренции с CISC?

Для начала разберемся с терминологией. CISC — это Complex (Complete) Instruction Set Computing (Полный Набор Команд). Формально к этому классу относятся в большей или меньшей степени все нынешние Athlon'ы, Pentium'ы и прочие процессоры для IBM PC совместимых компьютеров. В большей или меньшей потому, что те или иные заимствования идей и методов RISC имеются практически в каждом современном чипе. RISC — это Reduced Instruction Set Computing (Уменьшенный Набор Команд). Собственно название говорит само за себя: на основе статистического анализа кода множества CISC- приложений определяются наиболее часто используемые команды; уменьшение же числа команд позволяет увеличить число внутренних регистров (пересылка между регистрами выполняется быстрее всего), сделать конвейер более эффективным и поднять частоту его работы (чем более простые команды в нем исполняются, тем выше частота). Несмотря на значительно увеличившийся объем программного кода, RISC-процессор будет работать в несколько раз быстрее CISC-собрата с одинаковой частотой: специалисты всегда предпочтительнее универсалов (в плане быстродействия — уж точно). Разницу между RISC- и CISC-программами можно пояснить на простом примере. Но для начала оговорим некоторые детали: память компьютера адресуется по номеру строки и столбца, из которого осуществляется выборка (или в который производится запись). Операции над значениями из памяти производятся в исполнительном блоке, который, однако, может работать лишь с данными, загруженными в процессорные регистры. Пусть нам нужно умножить два значения в памяти по некоторым адресам 2:2 (строка:столбец) и 5:4. CISC нацелен на исполнение задачи при минимуме команд: набор инструкций процессора строится таким образом, чтобы все более или менее сложные действия решались одной командой. Предположим, что в CISC- процессоре имеется команда MULT, которая выбирает указанные значения из ячеек памяти, записывает их в различные регистры и сохраняет результат в соответствующем регистре. Тогда задача умножения решится в одну строку кода:

MULT 2:2, 5:4

RISC-процессоры используют простые инструкции, которые исполняются за один такт. В этом случае вместо MULT потребуются команды LOAD/STORE, загружающие данные из памяти в регистр и записывающие их обратно, а также команда PROD, выполняющая умножение данных в двух некоторых регистрах. Эквивалентом MULT для RISC-процессора будет следующий код:

LOAD A, 2:2

LOAD B, 5:4

PROD A, B

STORE 2:3, A

Таблица 1. Различия CISC и RISC

| СISC | RISC |

| Акцент на железо | Акцент на софт |

| Включает многотактовые сложные инструкции | Сокращенный набор однотактовых инструкций |

| Принцип "память-память" — работа с регистрами осуществляется автоматически | Принцип "регистр-регистр" — отдельные инструкции для передачи данных "регистр <-> память" |

| Небольшой размер кода, много циклов в секунду | Мало циклов в секунду, большой размер кода |

| Транзисторное пространство используется под размещение сложных инструкций | Транзисторное пространство используется для увеличения количества регистров |

В принципе, с увеличением объема кода можно мириться, если этот самый увеличенный объем позволит в несколько раз повысить быстродействие — пишут ведь на ассемблере? Пишут! Кроме того, RISC-код очень эффективно "распараллеливается"... В чем тогда причина непринятия RISC'а рынком IBM PC? Во- первых, как несложно догадаться, наборы инструкций CISC и RISC несовместимы. CISC-кода для PC-программ было написано очень много, а вот любителей писать под RISC на порядки меньше. Создавались, конечно, эмуляторы, автоматически транслирующие CISC-инструкции в RISC (подобные техники для увеличения скорости обработки используется в современных CISC-процессорах), но работали они настолько медленно, что разница в производительности между настоящими и эмулированными CISC практически сводилась к нулю. Таким образом, эмулировать CISC на RISC-процессорах оказалось неэффективно, а главное — экономически нецелесообразно.

Во-вторых, как следствие сыграла свою роль несовместимость ПО. Для х86 уже были написаны DOS и набирающая популярность Windows, а различные RISC- процессоры ютились на Unix, причем, как правило, на несовместимых между собой ее воплощениях. Да и программ для них было куда меньше, особенно пользовательских — все больше научные, специализированные.

В-третьих, несмотря на кажущуюся "упрощенность", RISC-процессоры были дороги — они выпускались сравнительно небольшими партиями для высокопроизводительных рабочих станций, и производители не считали нужным ни экономить на материалах, ни совершенствовать/оптимизировать дизайн, ни упрощать чипсет и материнскую плату. Крупные компании вроде Sun или DEC даже не задумывались об этих "мелочах", наивно полагая, что альтернативы их решениям отсутствуют. В некоторых сферах (научные ресурсоемкие вычисления), действительно, конкурировать с RISC системам на базе CISC-процессоров было сложновато. Зато во всех остальных недорогие и достаточно производительные x86-процессоры остались "на коне".

Тем не менее, жажда обойти Intel не давала покоя крупным полупроводниковым компаниям, и в 1991 году Apple, IBM и Motorola основали альянс AIM Alliance, который немедленно занялся созданием дешевого, быстрого и современного RISC-процессора. В 1993 году была представлена спецификация платформы PowerPC, а также первый чип — 32-разрядный PowerPC 601, работавший на частотах 50 и 66 МГц. Название PowerPC пошло от многочиповой RISC-архитектуры IBM POWER, на базе системы команд которой и был основан первый процессор. Чип рассеивал намного меньше тепла, чем его конкурент в лице Intel Pentium, и работал зачастую быстрее его. Вслед за 601-м появились 603/604 модели, затем в 1997 — PowerPC 750 (G3) с L2-кэшем и ускоренной системной шиной. В 1999 модельная линейка процессоров PowerPC пополнилась PowerPC 7400 (G4) — "конкурентом" Intel Pentium III, представившим поддержку набора команд для векторных вычислений AltiVec (также известного как VMX — Vector Multimedia eXtension — эдакое "мультимедийное расширение" PowerPC). Однако с появлением и совершенствованием архитектуры Intel NetBurst (в Pentium 4) процессоры компании закрыли единственное слабое место, которое позволяло PowerPC выглядеть более выигрышно: заметно ускорив операции с плавающей точкой, х86- процессоры оказались самыми быстрыми и дешевыми на рынке. PowerPC-чипы же остались уделом Apple Macintosh да различных встраиваемых систем (благодаря низкой рассеиваемой мощности) — системы на их базе, даже с учетом более дешевого процессора, все равно получались заметно дороже IBM PC совместимых компьютеров. Кардинальным образом ситуацию не изменил и выход нового процессора от IBM — PowerPC 970 (G5). Он позволил лишь приблизиться к x86 фаворитам в некоторых приложениях (и даже порой опережать их в оптимизированных), но не более того. Впрочем, не исключено, что герой этой статьи The Cell сможет вернуть RISC'у пальму первенства и создать предпосылки для появления популярной альтернативы долгоиграющей x86.

Пожалуй, один из главных инициаторов создания The Cell — подразделение Sony под названием Sony Computer Entertainment Inc. Еще с момента выпуска Emotion Engine ("сердца" PlayStation 2) SCEI не давали покоя мысли по более широкому его применению: например, объединение нескольких [десятков] EE демонстрировало солидную по тем временам (2000 год) производительность. Впрочем, прототип "числоперемалывателя" GSCube на основе 16 пар Emotion Engine и Graphics Synthesizer с 2 Гб RAM и 512 Мб видеопамяти оказался невостребованным из-за высокой цены и неавтономности (ему требовался для работы управляющий сервер SGI Origin 3400). Тем не менее, образованный в 2000 альянс IBM, Sony и Toshiba, засучив рукава, взялся за разработку не только мощного процессора для Playstation 3, но и универсального, многоцелевого и очень производительного продукта под кодовым названием Cell. Центр по разработке открылся на год позже (2001 г.) в Остине, штат Техас. Примерно в это же время, в марте 2001, патентное бюро США зарегистрировало патент и заявку на патент, в самых общих чертах описывавшие принципы функционирования Cell-структур. Изобретателями значились руководящие сотрудники SCEI, а правопреемниками — представители Toshiba и IBM.

IBM предоставила давнему дуэту по разработке специализированных чипов для Playstation в лице Sony и Toshibа свой солидный багаж технологий в области (в частности, метод"кремний-на-изоляторе" (Silicon On Insulator — SOI) для ускорения создания сверхмощных процессоров класса "система на чипе" (System On Chip — SOC). Ну и, конечно, производственные мощности. Sony с Toshiba — подключили лучшие умы для реализации интересных идей и наработок. Собственно, теперь, когда более четырех лет разработки (и миллиард с небольшим долларов, потраченный только на R&D) позади, а чипы уже производятся в ограниченных количествах на фабрике IBM в East Fishkill, когда информационный "железный занавес" троицы гигантов начал понемногу раздвигаться, можно поговорить о чипе более подробно. Несмотря на то, что сплошным "гаданием на кофейной гуще" (как в ранних зарубежных "аналитических материалах"), конечно же, нижеприведенная информация о структуре Cell не является, многие моменты (особенно связанные с реальным коммерческим воплощением чипа) остаются не проясненными до конца. Этот год обещает быть богатым на новости, связанные с Cell (особенно если учесть планируемый анонс Playstation 3 в мае), но не думаю, что фундаментальные концепции архитектуры будут изменены. Впрочем, довольно разговоров, пора уже взглянуть на

Сell изнутри

"Суперкомпьютер на чипе", как назвала Cell SIT в своей ISSCC-презентации, производится по 90 нм SOI-технологии с применением low-k-диэлектрика и восьмислойных межсоединений (low-k Intel реализует лишь в 65 нм техпроцессе c 7-ю слоями межсоединений). Первые тестовые образцы Cell представляют собой запакованные в стандартный BGA-корпус 42,5х42,5 мм (1236 контактов, из них 506 сигнальных, остальные — земля/питание) 234 млн транзисторов, образующих 9 "ядер" — основное, базирующееся на архитектуре PowerPC (PPE — Power Processor Element) и 8 векторных "доппроцессоров" (SPE — Synergistic Processor Element); остальные транзисторы реализуют интерфейс контроллера ввода/вывода (Flex I/O BIC, Bus Interface Controller) и памяти (MIC — Memory Interface Controller), а также, конечно, связывающую все элементы воедино внутреннюю шину (EIB — Element Interconnect Bus). Все это безобразие работает на частотах от 4 ГГц (хорошо, "должно работать на частотах от 4 ГГц";)) при напряжении питания от 1 В, обеспечивая при вычислениях с одинарной точностью (single precision) производительность более 256 гигафлопс!!! Если вы еще не свалились со стула, сообщу, что, к примеру, система на паре Intel Itanium 2 1,5 ГГц, демонстрирует лишь около 11-12 ГФлопс (миллиардов операций с плавающей запятой в секунду), а AMD Opteron 1,8 ГГц — около 4. Впрочем, к этой цифре (256 ГФлопс) стоит относиться с известным скептицизмом, однако даже если предположить, что SIT завысили реальную производительность (измерять ведь можно по-разному) в 10 раз, то все равно 25,6 ГФлопс для одного небольшого и легкомасштабируемого чипа — впечатляющее достижение.

Таблица 2. Сравнение характеристик прототипа Cell и современных х86-процессоров

| Процессор | SIT Cell | AMD Athlon FX-55 | Intel Pentium 4 660 | Intel Pentium XE 3,73 |

| Техпроцесс (нм) | 90, SOI, low-k | 130, растянутый кремний, SOI | 90, растянутый кремний | 90, растянутый кремний |

| Число транзисторов (млн) | 234 | 106 | 169 | 169 |

| Количество контактов | 1236 | 939 | 775 | 775 |

| Рабочая частота (МГц) | 4000-5300 | 2600 | 3600 | 3730 |

| Рассеиваемая мощность (Вт) | 80-180 | 104 | 115 | 115 |

| Площадь ядра (мм2) | 221 | 193 | 135 | 135 |

Cell изначально ориентирован на работу в симбиозе с другими "клетками". В идеале это выглядит так: когда Cell'ы некоторых объединенных в единую сеть устройств начинают простаивать, Cell'ы наиболее загруженных устройств перекладывают на "отдыхающих" часть своей работы, что выливается в заметное повышение производительности. Представьте, к примеру, что Cell'ам рабочей станции в сложном рендеринге "помогают" их собратья из игровой приставки, цифрового видеомагнитофона, ноутбука... Да, пока это кажется фантастикой, но все предпосылки для реализации "цифровой идиллии" есть. В теории возможности объединения аппаратных "клеток" не ограничены. А специально для обмена информацией между ними используются программные "клетки" — так называемые апулеты (APUlets, произошедшие от прежнего названия SPE — Attached Processor Unit, т.е. присоединенный процессор) — по большому счету, блоки, содержащие данные и описание тех действий, которые над этими данными необходимо произвести. Технология отдаленно напоминает программы распределенных вычислений типа SETI@Home, однако в каждом апулете будут содержаться не только данные для обработки, но и сам клиент-обработчик.

Рассмотрим все структурные элементы чипа по отдельности в подробностях (насколько это позволяют доступные источники информации). Итак, "ядром" каждой "клетки" является Power Processor Element, он же PPE. О ключевом элементе Cell'а, обеспечивающем "нагрузку" и управление SPE, взаимодействие с ОС, а также прочими "побочными" вычислениями, к сожалению, пока известно немногое. Это нечто выполненное на базе "64-битной Power-архитектуры" (на базе PowerPC 970? POWER 5? чего-то принципиально нового?) с поддержкой набора векторных мультимедийных расширений AltiVec и технологии многопоточности SMT (Simultaneous Multi-Threading) — судя по всему, некий аналог Hyper-Threading'а от Intel. PPE Cell, в отличие от последних x86-процессоров, не форсит мегабайтами кэша, но, похоже, 64 Кб L1-кэша (32 Кб для инструкций, 32 Кб — для данных) и 512 Кб L2-кэша ему вполне достаточно для получения приемлемой производительности.

PPE заправляет восьмью SPE, или Synergistic Processor Element. Эти "синергические" процессоры, по сути, являются специализированными независимыми векторными процессорами. Может возникнуть вопрос: что же это за векторные вычисления такие? В программистском понимании вектор — это упорядоченный список скалярных (-5, -3,999(9), 5.61, 18 и т.д.) значений. Соответственно, если мы работаем с векторами (массивами), то можем выполнять операцию над множеством данных одной инструкцией — это и называется SIMD (Single Instruction Multiple Data — один поток команд, множество потоков данных). Идея SIMD давно и успешно применяется как в специализированных системах, так и в Mac'ах (AltiVec), и в PC (SSE-SSE3, 3DNow!...). Продемонстрируем удобство векторных вычислений на вполне жизненном примере. Итак, пусть у нас имеются три вектора-массива по N элементов в каждом: А, В и C. Необходимо сложить соответствующие значения в массивах А и В, записав результат в массив С. Если код не будет "векторизован" компилятором, то процессор будет поочередно выбирать по одному значению из А с В, затем складывать эти значения, записывать результат в С, выбирать следующее значение из А с В... И так — N раз. Если же код будет векторизован, процессор сможет не тратить "лишние" такты на манипуляции с единичными значениями; векторы А и В будут считаны из памяти целиком, операция векторного сложения их сложит "единовременно" (c минимальной задержкой на поступление очередной пары значений в вычислитель), а по окончании операции вектор-результат С будет записан в память "за один присест".

Если подключить воображение и предположить, что с векторами нужно проделать не одну, а несколько операций (это актуально для графических приложений с различными матричными преобразованиями), то выигрыш в производительности благодаря "одновременной" работе со всеми значениями становится очень и очень значительным. Тем не менее, далеко не всякий код можно "векторизовать": препятствием на пути солидного ускорения станет и одномерная рекурсия, и сложные условные переходы, и специфичность алгоритмов... В общем, векторизация и векторные вычисления — вещь хорошая, позволяющая достичь большой скорости исполнения программы... но лишь в тех случаях, когда код под это "заточен". В противном случае никаких дивидендов от векторных команд добиться не получится.

Но вернемся к нашему "восьмиединому" векторному SPE. По сути, он представляет собой классический векторный (но, в отличие от традиционных "векторников", независимый) процессор с длиной команды в 32-бита и размером вектора в четыре 32-битных слова. При этом каждое из слов обрабатывает "свой" целочисленный блок или блок по работе с плавающей запятой (FPU — Floating Point Unit). Каждый SPE обладает 128 (!) 128- разрядными регистрами и небольшим объемом (256 Кб) локальной памяти, разделенной на 4 адресных пространства по 64 Кб. Так как память фактически объединена с процессором, вопрос кэша для выравнивания их (процессора с памятью) производительности не ставится. Но хватит ли 256 Кб для эффективной обработки апулетов? По идее, этого объема должно быть вполне достаточно (а для апулетов-шейдеров — и подавно), но пока делать окончательные выводы рановато. С внешней же памятью SPE может "общаться" через Memory Interface Controller с применением механизма DMA (Direct Memory Access — прямой доступ к памяти) — то есть напрямую, без посреднических услуг PPE. Ну и для завершения "портрета по фотографии" основной движущей силы Cell — Synergistic Processor Element'а — необходимо добавить, что каждый SPE можно динамически "закрывать" и "открывать" для защиты внутренних ресурсов от доступа извне (опять-таки, точный принцип действия этого механизма пока неизвестен), а также что SPE в своем наборе инструкций не имеет поддержки AltiVec (VMX). Следовательно, общая производительность при использовании этих расширений будет определяться лишь одним PPU. Возможно, при этом будут задействованы и SPE, но "родная" поддержка векторного набора команд упростила (и ускорила) бы процесс. Таким образом, SPE представляет собой достаточно мощный, но в то же время узкоспециализированный процессор. Если программист (при помощи компилятора) сумеет добиться от него полной отдачи, эффективно загрузив "апулетами", производительность резко подскочит. В противном случае, боюсь, при исполнении невекторизованного кода заметного прироста производительности даже от 16 SPE (по большому счету, количество SPE в Cell ограничивается лишь технологическими ограничениями при производстве кристаллов) ждать не стоит.

Все ключевые элементы чипа (8 SPE, PPE, MIC и BIC) cвязаны между собой высокоскоростной шиной EIB — Element Interconnect Bus. Она четырьмя кольцами "опоясывает" все блоки структуры, позволяя передавать до четырех 128-битных слов одновременно (!!!) с пиковой пропускной способностью 96 байт/сек. Именно с ее помощью апулеты из PPE "разбрасываются" по SPE или кочуют между ними, отправляясь по мере готовности в память. Шина EIB позволяет инженерам гибко наращивать число SPE в случае необходимости (для модифицированных версий чипа, очевидно).

Структурная схема Cell-чипа

За связь с "внешним миром", а в частности — с таким важнейшим элементом, как RAM (т.е., оперативная память), отвечает Memory Interface Controller, или MIC. Для своего детища инженеры SIT лицензировали сверхбыструю XDR RAM от Rambus (да, уже можно представить, сколько ЭТО будет стоить). Двухканальная XDR RAM на 4-х чипах позволит обеспечить пропускную способность порядка 25 Гб/сек! Кроме того, контроллер умеет закрывать доступ к определенным фрагментам памяти конкретным SPE. К сожалению, пока на рынке представлены максимум 512 Мбит чипы памяти, а следовательно — общий объем RAM не сможет превысить 256 Мб. Однако ходят слухи о том, что контроллер XDR RAM может работать и в другом ("серьезном") режиме, поддерживая до 32 Гб памяти с коррекцией ошибок (ЕСС). Впрочем, за столь высокую скорость (традиционная PC3200 обеспечивает пропускную способность лишь порядка 3,2 Гб/сек) неизбежно приходится платить. В данном случае — предсказуемо высокой ценой и сравнительно небольшой емкостью чипов. Контакт с внешними устройствами (и, похоже, с другими Cell) обеспечивает еще одна лицензированная разработка Rambus — шина Flex I/O и ее контроллер Bus Interface Controller. Она обеспечивает огромную пропускную способность (44,8 Гб/сек на передачу, 32 Гб/сек на прием), а также использует фирменные технологии снижения тепловыделения DRSL (Differential Rambus Signaling Level — дифференциальный уровень сигналов Rambus) и упрощения топологии схемы FlexPhase. Очевидно, что для Cell имеются хорошие возможности для объединения — было бы с чем;)! Все чипы, работающие на высоких частотах, неизбежно сталкиваются с одной проблемой — тепловыделением. Будь процессор хоть трижды суперпроизводителен, он вряд ли получит распространение в мире, если для его охлаждения потребуется установка на жидком азоте. Контролируют питание, нагрев и энергопотребление Сell'а встроенная система динамического управления мощностью Dynamic Power Management (DPM автоматически выбирает одно из пяти состояний управления питанием), а также 10 цифровых и один линейный термодатчик. Так что гибкости и средств мониторинга Cell'у явно не занимать. При этом, по неофициальной информации, 4 ГГц чип рассеивает 80 Вт (1,1 В), а старший 5,3 ГГц вариант (1,3 В) — 180 Вт. С переходом на более совершенный 65 нм техпроцесс SIT планируют снизить тепловыделение до 30-40 Вт для 4,6 ГГц чипа Cell. И такие цифры (как тактовой частоты, так и рассеиваемой мощности) выглядят, разумеется, крайне привлекательно.

Что можно сказать в заключение "брифинга" по архитектуре The Cell? Процессор, безусловно, обладает рядом интереснейших особенностей, позволяющих прочить ему большое будущее. Мощнейший контроллер памяти, "бесконечная" расширяемость, многоядерность, технология апулетов и раздельных спецпроцессоров... Пока (и, к сожалению, лишь на бумаге) The Cell выглядит впечатляюще. Не стоит забывать, однако, сколько раз амбициозные высказывания разработчиков оказывались, гхм, "преувеличенными", а также сколько раз непобедимую глыбу CISC безуспешно пытались "убить" RISC- процессоры. Да, на оптимизированном коде по производительности вряд ли кто-то сможет что-то противопоставить Cell, но как быть с обыкновенными, не оптимизированными, приложениями? С огромным количеством CISC-программ? Будут ли они эмулироваться, переноситься? Насколько это будет выгодно с экономической точки зрения?.. Кроме данных насущных вопросов, уверен, всплывет и еще одна извечная проблема RISC — цена. Очевидно, что Cell — очень сложный чип, да и компоненты для него вряд ли будут простыми и дешевыми (одна память чего стоит!). Поэтому возникает основополагающий вопрос: сможет ли SIT производить Cell в таких количествах, чтобы удерживать цены на разумном и конкурентоспособном уровне? Судя по тому, что Playstation 3 вряд ли будет стоить более 500 у.е. даже в первые месяцы, сам Cell не будет очень уж дорог — Sony нет смысла работать себе в убыток. Впрочем, не будем гадать, а лучше поговорим о возможных сферах применения Cell и сделаем предварительные оценки его потенциала в каждой из областей.

Cell'и Cell'а

Первой и важнейшей (для SCEI;)) сферой применения нового чипа станет давно ожидаемая (но до сих пор не анонсированная) игровая приставка нового поколения — Sony Playstation 3. По слухам, в ней будут работать аж 4 Cell'а на тактовой частоте 4,6 ГГц. Честно говоря, это выглядит слишком фантастично; куда реальнее будет наличие одного 4-гигагерцевого Cell'а и низковольтной "клетки поддержки". Дело в том, что четыре 4,6 ГГц Cell'а будут рассеивать вкупе с мощнейшим графическим чипом... гхм... очень много тепла. Сомнительно, что Sony станет позиционировать PS3 еще и в качестве портативного обогревателя;) — именно поэтому, скорее всего, количество Cell будет ограничено. В противном случае Sony придется применять уж очень нестандартные охладительные решения, чтобы эффективно отводить около 500 Вт, выделяемых всеми этими замечательными устройствами. Но даже если в PS3 будет один Cell, его производительности создателям игр хватит надолго. Ведь фактически каждый SPE есть подобие Emotion Engine из PS2, да еще и с "бесплатным приложением" в форме PPE... На мой взгляд, SPE смогут достаточно уверенно работать с вершинными шейдерами, заниматься обсчетом игровой физики, звука, а на PPE будут возложены "задачи поддержки". Пусть эффективно программировать Cell, скорее всего, будет не легче, чем EE+GS (PS2), мучения программистов с лихвой будут компенсированы огромным вычислительным потенциалом "клетки". PS3 наверняка сможет уверенно работать с DVD, видео, телевидением высокой четкости (HDTV — High Definition TeleVision) а также прочими "цифро- домашними" приложениями.

Как следствие еще одно важное направление для применения чипа (в котором заинтересована не только Sony, но и Toshiba) — бытовая электроника. "Умные" видеомагнитофоны, исключительно "сообразительные" телевизоры, недорогие и высокоэффективные мультимедиацентры... Простор для использования Cell на этом поприще удивительно широк. Разумеется, светлое будущее ждет новые чипы лишь в том случае, если они будут: а) сравнительно недороги, б) "холодны" и в) сопровождаться удобным инструментарием для программирования.

Далее. Cell'ы отлично будут чувствовать себя в специализированных рабочих станциях и "недорогих" суперкомпьютерах. Благодаря отличной заявленной масштабируемости и производительности для задач, скажем, специфической визуализации, разнообразных ray-tracing-алгоритмов, научных вычислений (даже с двойной точностью) Cell сможет прочно обосноваться и в этой нише. Опять-таки, для этого необходимо соблюдение многих условий (например, решение вопроса с объемом памяти), но так или иначе вероятность того, что чип приживется в традиционно RISC'овой нише крайне велика. Несмотря на обилие "специалистов", прочащих Cell в очередные "убийцы х86", очевидно, что платформе Wintel в ближайшее время ничто не угрожает. В идеальном для SIT случае Cell'ы постепенно вытеснят продукты Intel/AMD с рынка. Однако для достижения этого необходимо преодолеть большое количество "но": Cell должен или быстро обзавестись собственным большим набором софта, или научиться очень эффективно эмулировать CISС; кроме того, должен быть создан удобный и эффективный инструментарий для создания программ (желательно — язык высокого уровня), позволяющий использовать преимущества архитектуры Cell "по полной". Вдобавок, повторюсь, Cell-системы должны продаваться если не по низким, то хотя бы по средним (до 1000 у.е.) ценам — дорогие и несовместимые системы х86 пережует и выплюнет вообще безо всяких усилий. Значительно более вероятно, что на РС Cell будут успешно применяться в качестве специализированных прикладных "числодробилок". Например, для цифровой обработки сигналов (алгоритм быстрого преобразования Фурье легко векторизуется), графических нужд (при необходимости Cell, судя по всему, сможет успешно работать в качестве GPU), аудиообработки — PCI Express карта расширения с чипом (-ами) Cell послужит хорошим дополнением к Pentium'у/Athlon'у. Но, опять- таки, для этого нужен серьезный инструментарий для разработчиков (говорят, IBM активно работает над SDK), качественные драйверы, разумные цены... Перспективно ли это? Безусловно! Возможно ли это? Пока трудно сказать. Если SIT планируют серьезно двигать свое детище в массы — разумеется, да. Если же после дебюта в PS3 SIT развитие Cell затормозят (по всем направлениям), то на эттом чипе можно будет смело ставить крест.

Как минимум еще одна компания должна в данный момент тщательно изучать Cell — это Apple Computers. Так как IBM пока еще работает над последователем мощного PowerPC 970, Cell может стать неплохой альтернативой для применения в Mac'ах. А может и, чем Джобс не шутит, достойным G6. Cell поддерживает AltiVec (VMX) — пусть производительность этих расширений вряд ли будет выдающейся (т.к. обрабатывать их умеет лишь PPE) — Apple наверняка сможет получить свои дивиденды от архитектуры Cell — масштабируемости, производительности, многопоточности и многоядерности.

Новый бестcellер?

К сожалению, на вопрос, вынесенный в заголовок статьи, еще нельзя ответить однозначно. Да, "стелит" альянс гигантов мягко, но вот будет ли так же мягко "спать"? По характеристикам, идеям и технологиям Cell — однозначный прорыв в микропроцессорной индустрии. Впрочем, направление прорыва станет известно позднее;). Станет ли Cell обыденным компонентом бытовой техники? Найдет ли применение в рабочих станциях? Останется ли "замурованным" в Playstation 3? Попадет ли под крыло Apple? Сможет ли стать хорошим строительным материалом для создания суперкомпьютеров? "Убьет", будет смят или сумеет мирно сосуществовать с x86-процессорами?.. Каким образом разрешится эта интрига, а также кто из аналитиков- Нострадамусов, задающихся подобными вопросами, окажется прав, мы узнаем в ближайшие пару лет. А пока можно констатировать лишь одно: на стапелях SIT разрабатывается и уже производится крайне интересный продукт, который, возможно, перевернет устоявшийся рынок микропроцессоров. Возможно, однако, что чип будет столь же "популярен", как и Emotion Engine PlayStation 2 и многие другие RISC-продукты... Поживем — увидим! Так что следите за новостями — теперь слово "Cell" будет мелькать в них все чаще и чаще!!

Николай "Nickky" Щетько,me@nickky.com

Компьютерная газета. Статья была опубликована в номере 11 за 2005 год в рубрике hard :: процессоры